本文根据台湾一大公司的设计指导文件结合自己的一些经验与理解,和大家探讨一下PCB布局中的一些生产工艺方面的要求。在PCB布局注意一下这些要求,可以避免很多不必要的麻烦。

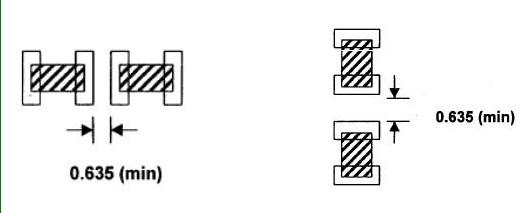

1.SMD元件LAYOUT最小间距。SMD LAYOUT时保证一定的元件间距可以减小焊接时出现虚焊、桥连、阴影效应等问题的概率。

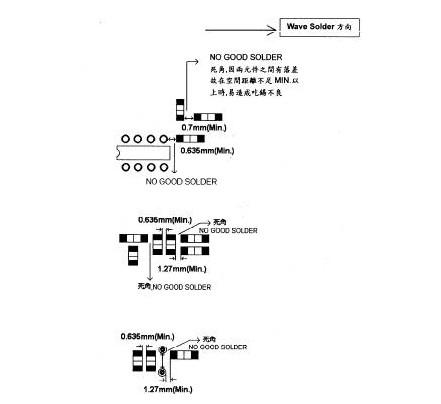

图1、元件水平间距 图2、元件垂直间距

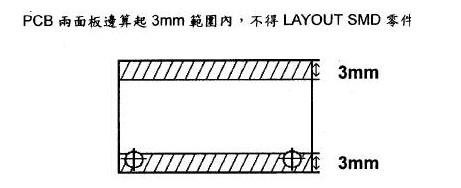

2.SMD PCB两面板边算起3mm范围内,不应LAYOUT SMD元件。这主要是因为贴片机的导轨槽要求PCB板边3~5mm内不允许有元件存在。3mm是最小要求,如果实在不能保证这个尺寸,可以考虑采用V型槽或邮票孔来加长板子,等焊好后再将多余的板子撇掉。

图3、SMD PCB板边要求

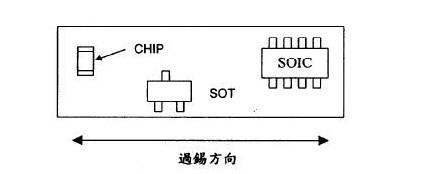

3.SMD排列方向。

(a) 相同的元件,排列方向尽量一致。

(b) 在同一条金道上,必须留一个测试点,直径30mil。

4. SMD与PTH器件混装,且采用波峰焊一次焊成时,

(a) CHIP、SOT、SOIC元件排列方向尽量和过锡方向垂直,以避免阴影效应。

(b) 本体高度相差太大的元件,不可紧靠排列,以避免阴影效应。

(c) 任何元件最好均能做平行排列,且和过锡方向垂直。

阴影效应是采用波峰焊的方式来焊接SMD元件时,PCB布局所必须考虑的,如果采用回流焊的话,就没有这个问题了。所谓阴影效应,举个例子来说,有元件高度相差很大的两个SMD元件紧靠在一起时,如果高的元件先过锡,就有可能因为高体元件的抵挡使得后过锡的低体元件吃不到锡,这就是高体元件的阴影影响。

图4、采用波峰焊时元件排列

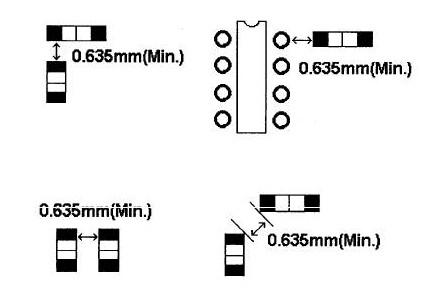

(d)必须做直角(垂直)排列时须保留足够的吃锡空间,此空间距离应为0.635mm。

图5

5.SMT LAYOUT造成焊锡死角(空焊)

下图给出了可能造成空焊的情况。具体LAYOUT时,须要自己多考虑该布局在焊接时是否可能造成空焊,总而言之,须要灵活应用,不可生搬硬套。

6.V-CUT参考数据

(1) FR-2,CME-1,OAK910(半玻璃纤维)PCB厚度1.6mmV-CUT切刀的深度为0.4mm×2面。

FR-4 PCB厚度1.6mm V-CUT切刀深度0.5mm×2面。